In the race to increase chip density, integrated device makers (IDMs) like Intel and AMD have lost to TSMC. To regain the lost glory, they have been desperate. To overcome the growing complexity and cost of successive process nodes, they are after alternatives to the monolithic design approach. In this mission, they are after chiplet technology—to make chips as a collection of chiplets. They are after creating a new wave of Creative Destruction to monolithic chip fabrication by pursuing a modular approach.

Chiplet technology is not new. As early as 1965, IBM used it in developing a large processor. It remained dormant for quite a long time before gaining popularity from AMD’s use of Chiplet technology. Due to the growing complexity and cost of moving to the next process nodes, chip makers are after this old technology. In 2015, AMD’s design of the Ryzen processor with chiplet technology resulted in a 40% cost reduction. Since then, there has been a growing interest in chiplet. Speculation surfaces that chiplet technology may rise as a new wave of creative destruction to monolithic design.

A Chiplet is a tiny integrated circuit. Instead of being a full-function processor, it contains a well-defined subset of functionality, such as a graphics processing unit (GPU). Chiplet keeps gaining popularity due to the increasing complexity and cost of making sizeable monolithic semiconductor chips. Hence, Chiplet technology is on the rise redefining the semiconductor industry. Chiplet technology progresses to fragment a monolithic chip into function-specific multiple chiplets. These chiplets are produced with different process nodes and interconnected on an interposer in a single package. Hence, a large chip is created by integrating many chiplets instead of a single monolithic die. But due to trading off performance for cost saving, does chiplet technology ends up being a weak core for Reinvention?

Economics of chiplet technology

Since the publication of Moore’s law in 1965, the race in the semiconductor industry has been to increase the Transistor count on each chip. It kept rising from 2,250 transistors on a 12mm2 die in Intel 4004 to 57 billion transistors on M1-Max, which has a 432mm2 die. As the shrinking of transistors kept reducing per transistor cost and improving performance, increasing chip density became the core competition strategy. But due to exponentially growing capital expenditure and falling yield, this race has started to lose momentum—raising chiplet technology’s economic viability.

In 1963, Fairchild was selling transistors (part number 1211) to military customers for $150 each. Its small volume of production cost was $100 apiece, leaving a healthy $50 profit. If the semiconductor industry did not succeed in reducing this cost figure, what could have been the price of Apple’s A15 bionic chips containing $15.8 billion transistors powering the iPhone? Even after 13 years, in 1976, 16 Kb DRAM used to cost $10. Extrapolation of this number for typical 16GB (16Gb x 8) memory used in consumer PCs today would cost about $80 million for the memory chips.

Besides, the PCB to integrate all those 16Kb DRAM chips to form 16GB memory would be about 37,000 square feet. Furthermore, the memory unit would consume approximately 3,500,000 Watts of electricity, costing over $250,000 (At $0.10 per KWh)per month to power this memory board. Of course, we should consider additional issues like access time, bandwidth, reliability, etc.

Economics kept driving higher chip density–giving birth to Moore’s Law

But as we keep increasing the number of transistors on the same die by decreasing the size, all those cost and performance indicators start getting in favor. Hence, the focus began on improving means of higher chip density. As a result, the transistor dimension kept falling, and the die size kept increasing.

For example, in 1972, Intel 8008 processor had 250 transistors per mm2, followed by Corei7 in 2008, containing 3,007,760 transistors per mm2. Die size also kept increasing from 14mm2 die for 8008 to 263mm2 die for Corei7. To succeed in exponentially growing transistor density, die size, and transistor count per die, the process node kept shrinking from 10,000nm fabrication technology for 8008 to 45nm used to produce Intel Corei7 in 2008. It kept falling, reaching TSMC’s 4nm to make Apple Bionic A15 in 2021.

This remarkable journey of reducing transistor size and increasing chip density resulted in doubling the transistor count on a single die over 18 to 24 months. Gordon Moore predicted it in his 1965 paper, giving birth to Moore’s Law.

Growing capital expenditure and falling defect size—raising the popularity of Chiplet

The journey of keeping Moore’s Law alive kept increasing capital expenditure in terms of fab cost and reducing the tolerable defect size. But as the marginal cost per transistor kept falling, moving to the next process node became economically attractive. But the growing fab cost and falling defect size have been showing the limit. For example, a 5nm fab costs as much as $15 billion, which increases to $18 billion for a 3nm node. Furthermore, the tolerable defect size has fallen, reaching 1nm in a 5nm node (roughly 20% of the size of the fabrication node). As a result, yield, as a measure of defect-free chip count, has been falling, resulting in increased costs. Hence, the increasing cost has been surfacing as a barrier to moving with higher chip density and die size. Consequentially, economics has been increasingly favoring chiplet technology.

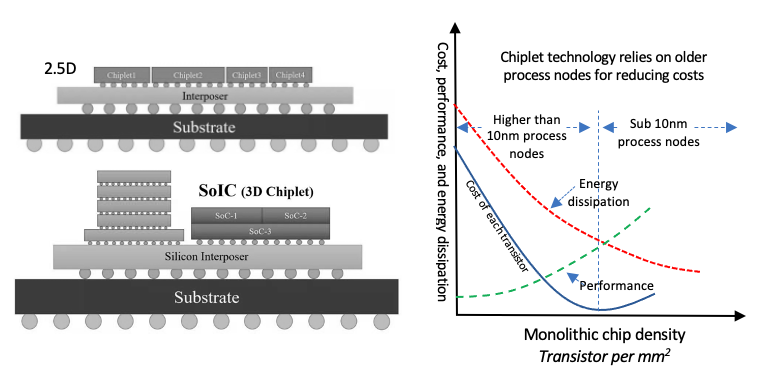

Unlike Moore’s Law era, chiplet technology faces cost and performance trade-offs

As Chiplet technology relies on older fabrication processes, they will enjoy lower fab costs and higher yield than the latest process node. But such a gain will emerge at the expense of giving up quality. For example, a 7nm node fab costs far less than a 3nm node. Yield will also be higher due to the larger tolerable size of defects. But as Samsung reports, 3 nm GAAFET delivers a 35% performance increase, 50% power reduction, and a 45% reduction in the die area compared to 7 nm. So, if you produce chiplets using a 7nm node to make a large chip, there will be significant performance loss and higher energy dissipation. Besides, it will require double the wafer area, resulting in higher processing costs. Hence, for performance, energy, and space constraint applications, Chiplet will find in a disadvantageous position.

In wearable and mobile computing applications, performance, energy dissipation during operation, and chip size highly matter. Even for data center applications, energy dissipation footprint is a big issue. Therefore, AMD’s reported 40% cost reduction out of Chiplet results from accepting far less performance and higher energy dissipation. Hence, a trade-off issue will influence the adoption of chiplet. But in Moore’s law era, semiconductor innovators enjoyed lower cost, higher performance, less power dissipation, and higher transistor count per mm2 die for moving to the next node.

Defining Chiplet technology

Chiplet technology refers to (i) designing a large chip as chiplets, (ii) fabricating each of them using appropriate process nodes (invariably older), and (iii) packaging them as a single chip. Chiplet technology promises to offer a menu of modular dies, or chiplets, in a library. Each of them will have different functions. They will likely be produced using different process nodes; a single chip may have chiplets made using 7nm, 10nm, 28nm, and 45nm nodes. Furthermore, chiplets products using different technologies such as silicon, InP, and SiC could be packaged together as an extensive system on integrated chips (SoICs). Of course, Chiplet technology also includes substrates to incorporate the devices and means to enable interconnects for these devices. To address substrate and interconnect, optics, copper hybrid bonding, standardized interconnects, and many other technologies are under development.

Types of Chiplet packaging technology

In terms of dimensions, there are two packaging approaches: 2.5D and 3D. 2.5D refers to the integration of methods using an interposer. Individual chiplets are placed horizontally on the same plane while the interposer connects them with the substrate. Instead of an interposer, 3D packaging refers to the direct high-density interconnection of chips through TSV. In 3D packaging, chiplets are placed on top of one another, forming a 3D structure like a multistoried building, each chiplet occupying a layer. Finally, interposes connects the 3D assembly of the Chiplet with the substrate. SiP (System-in-Package) refers to forming a system in a package, whether using 2.5D or 3D packaging.

Major companies pursuing Chiplet

AMD: Through Ryzen and Epyc chips, AMD has been benefiting from chiplet technology for years. Experts claim that AMD has reinvented itself by changing the monolithic approach of producing large chips with chiplet technology. By breaking apart each big chip into smaller ones, Engineers solved many critical problems like yield and 850 mm2 die size limit. As a result, the cost of AMD’s chiplet-based server chips, released in 2015, came down by 40%, giving AMD a way to compete with Intel in the server market. Furthermore, it allowed AMD to make an entire lineup of server products without redesigning a chip for the end market. Besides, AMD also leveraged chiplets for desktop processors.

By leveraging recent advancements in chip fabrication and interconnect technology, AMD envisions offering custom-built chips to its major customers. AMD customers could choose and pick from its IP portfolio to have appropriate chiplets to meet their requirements optimally. The recently introduced Universal Chiplet Interconnect Express (UCIe) standard opens further opportunities for AMD to integrate 3rd party chiplets.

Intel: As part of its comeback plan, Intel is pinning its future on 2D and 3D multi-die packaging technologies. By the way, Intel is not new in the Chiplet era. As early as 2005, Intel combined two CPU cores as a single Pentium D processor. It again used Chiplet technology with its 1st generation core “Arrandale” processors. Over the years, Intel has been improving interconnect technology to reduce the negative effect on bandwidth between chiplets and power. One of the notable examples of Intel’s Chiplet technology use is the fabrication of “Ponte Vecchio” chip combining 47 chiplets (containing 100 billion transistor). Intel plans to use the same interconnect technology for its upcoming Meteor Lake and Arrow lake processors.

TSMC: TSMC has been extending pure-play foundry by facilitating and offering chiplet services. TSMC has been instrumental in forming the 3DFabric alliance to make it easier for its clients, fabless chip companies. It will help chip designers implement advanced chiplet packaging technology. Furthermore, the 3DFabric alliance brings diverse partners from EDA tools and memory to substrates and testing. TSMC offers a 3D fabric portfolio of 3D silicon stacking and advanced packaging technologies. TSMC’s 3DFabric portfolio offers advanced technologies like SoIC and older technologies like integrated-fan-out and chip-on-wafer-on-substrate (CoWoS).

Rise of Chiplet as a creative force of destruction

Modular design and fabrication of chiplets using older process nodes offer a less costly way to make complex chips with billions of transistors. It reduces product development time and cost by integrating pre-developed dies in an IC package. Chip makers will get a menu of chiplets or die having different functions at various nodes, developed by many firms. Hence, customers can mix and match the chiplets and connect them using a die-to-die interconnect scheme. Of course, there are benefits, but at a cost.

Instead of getting monolithic chips processed using the latest process node, the IC packages out of the integration of chiplets produced using older nodes suffer from multiple limitations. Notable ones are (i) performance, (ii) latency, (iii) heat dissipation, and (iv) size of the package. Hence, unlike Moore’s law era, the chiplet era does not simultaneously offer cost and performance benefits. Here is a trade-off issue.

Despite the success of AMD’s chips in the server market, many applications will find cost-saving less attractive than giving up other benefits. For example, size and power consumption highly matter for wearable and mobile devices. In some internet of thing (IoT) applications, a tiny battery should last years to power chips. In such an application, a slight variation in power consumption will significantly determine the comparative advantage. Hence, chiplet technology fueling the creative wave of destruction will depend on applications. For desktop computing and small data centers, processors out of Chiplets may have cost advantage. But monolithic design using the latest process nodes may have a higher comparative advantage for mobile and wearable computing. Besides, chiplet technology increases the importance of OSAT or packaging services providers and fabless chip companies. Hence, IDMs may risk suffering from the creative destruction of Chiplet technology—due to invasion threat.

A weak technology core for reinvention–due to trading off performance

Unlike integrated circuits following Moore’s Law or digital cameras, chiplet technology trades off performance for cost savings. Hence, at best, chiplet technology core appears to be a cost-saving alternative for applications not requiring high performance. Therefore, IDMs producing chips for traditional applications like desktop applications may end up gaining cost savings. But the chiplet technology core will unlikely grow as a strong technology core unleashing creative destruction force on monolithic chip design approach for performance-sensitive applications. Historically, no technology core has succeeded in fueling reinvention waves by trading off performance for cost. Hence, IDMs will unlikely regain their glories by reinventing their chip design and making through chiplet technology core.

...welcome to join us. We are on a mission to develop an enlightened community for making the world a better place. If you like the article, you may encourage us by sharing it through social media to enlighten others.

Related Articles

- Chip War

- ASML–growing pearl gets caught in Chip War

- China’s Semiconductor Independence–prematurely caught?

- India’s Semiconductor Dream–pushed in the slow lane?

- Semiconductor Value Chain–globally distributed ecosystem

- Semiconductor IndustryWaves

- Intel Falling Due to PC and Mobile Waves

- ASML Lithography Monopoly from Sustaining Innovation

- Taiwan’s Semiconductor Monopoly – How did it arise?

- ASML TSMC Nexus Fuels Semiconductor Monopoly

- ASML Monopoly in Semiconductor — where is magic?

- SEMICONDUCTOR MONOPOLY DUE TO WINNING RACE OF IDEAS

- Semiconductor Industry Growth–personalities, new waves, and specialization underpin

- Transistor–technology core shaping global trade and power